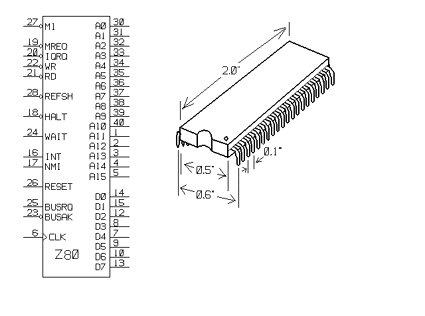

A0 à A15

Bus d'adresse tristate en sortie actif à l'état haut sur 16 bits . A0 est le bit le moins significatif ( LSB ) et A 15 le bit le plus significatif ( MSB ) D0 à D8

Bus de donnée tristate en entrée/sortie actif à l'état haut sur 8 bits . D0 est le bit le moins significatif ( LSB ) et D7 le bit le plus significatif ( MSB ) M1

Sortie active à l'état bas, signale que le cycle horloge courant est consacré à une identification d'op-code ou qu'un IORQ est actif . MREQ

Sortie tristate active à l'état bas . Signale que le bus d'adresse est en attente d'une adresse pour lire ou écrire en mémoire . IORQ .

Sortie tristate active à l'état bas . Signale l'un des deux événements suivants :

— La partie de poids faible du bus d'adresse est en attente d'une adresse pour lire ou écrire en mémoire .

— Un vecteur d'interruption peut-être placé sur le bus de donnée pour être acquis. RD

Sortie tristate active à l'état bas . Signale que le CPU veut lire des données en mémoire ou sur un périphérique WR

Sortie tristate active à l'état bas . Signale que le bus de données contient une donnée qui peut être stockée en mémoire ou envoyée vers une périphérique . RFSH

Sortie active à l'état bas . Indique que les bits de poids faible du bus d'adresse contienne une adresse de rafraîchissement des RAM dynamique . HALT

Sortie active à l'état bas . Indique qu'une instruction HALT a été exécutée par le CPU . Ce dernier est en attente d'une interruption . Pendant ce temps, il exécute des nop pour pouvoir rafraîchir ses RAM dynamiques . WAIT

Entrée active à l'état bas. indique que la mémoire ou le périphérique n'est pas prêt à être accédé. INT

INT est générée par un périphérique pour signaler qu'il désire qu'on s'occupe de lui. La requête prendra effet à la fin de l'exécution de l'instruction courante si le flag IFF est valide et si BUSRQ est inactif NMI

Entrée active sur fond bas. Cette demande d'interruption est plus prioritaire que INT. Elle est prise en compte quel que soit l'état du flag IFF. Cette interruption débranche le CPU à l'adresse 0066H. Le PC est automatiquement sauvegardé, et la sortie d'interruption ramènera le PC à l'endroit ou il avait été sauvegardé. RESET

Entrée active à l'état bas. Le PC est mis à 0 et le CPU est initialisé : IFF = 1, I = 0, R = 0, IM = 0. Pendant la phase de reset, les bus de données et d'adresses sont dans l'état tristate. BUSRQ

Entrée active à l'état bas. Signale qu'un périphérique demande un accès aux bus de données, d'adresses et signaux de contrôles. Ces diverses pattes vont passer dans un état tristate. BUSAQ

Sortie active à l'état bas. Signale que le bus d'adresses, de données et les signaux de contrôle sont dans un état tristate, et que le périphérique qui a demandé de les contrôler peut le faire dès à présent. CLOCK

Horloge de cadencement du microprocesseur.

| ★ AMSTRAD CPC ★ DOWNLOAD ★ |

|

CPCrulez[Content Management System] v8.732-desktop

Page créée en 229 millisecondes et consultée 1482 foisL'Amstrad CPC est une machine 8 bits à base d'un Z80 à 4MHz. Le premier de la gamme fut le CPC 464 en 1984, équipé d'un lecteur de cassettes intégré il se plaçait en concurrent du Commodore C64 beaucoup plus compliqué à utiliser et plus cher. Ce fut un réel succès et sorti cette même années le CPC 664 équipé d'un lecteur de disquettes trois pouces intégré. Sa vie fut de courte durée puisqu'en 1985 il fut remplacé par le CPC 6128 qui était plus compact, plus soigné et surtout qui avait 128Ko de RAM au lieu de 64Ko. |

|

|