| ★ CODING ★ CHRONIQUE Jean-Pierre Richard pour l'Ordinateur Individuel ★ Les opérations arithmétiques: de la multiplication aux entrées-sorties ★ |

| L'Ordinateur individuel n°22 - Les opérations arithmétiques: de la multiplication aux entrées-sorties |

Nous voici parvenus à la fin de cet exposé théorique sur le langage machine et l'assembleur pour le Z-80. Après avoir vu les« dernières » opérations disponibles, il ne vous restera plus qu'à pratiquer. Bon courage ! Multiplication et division en «binaire» seront étudiées après les opérations de décalage et de rotation. Les instructions de comparaison du Z80 sont de deux types : comparaison simple ou recherche par comparaison. L'opération de comparaison confronte le contenu de l'accumulateur (a) avec l'octet dans un registre r (r peut être B, C, D, E, H ou L) en effectuant la soustraction a-r. Le résultat modifie les indicateurs d'état C, Z, P/V et S. L'instruction CPr permet un test semblable au test du BASIC : A supérieur, égal, inférieur ou différent de r. Les contenus de l'accumulateur et du registre ne sont pas modifiés par cette opération. Le sous-programme présenté ci-dessous teste et dirige le programme principal vers SPRGR1 si A est égal à C (Z = 1 ) ou vers SPRGR2 si A est différent de C : CP C ; A - CCet autre petit sous-programme teste le registre D et branche le programme principal à l'adresse SPRGR3 si A est inférieur à D, à l'adresse SPRGR4 si A est égal à D ou à l'adresse SPRGR5 si A est supérieur à D. |

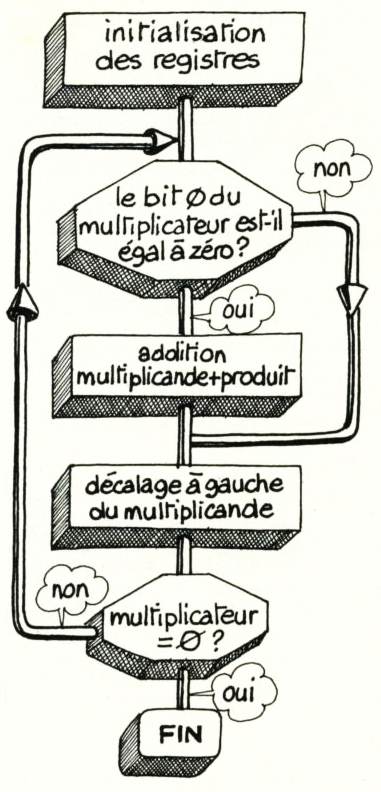

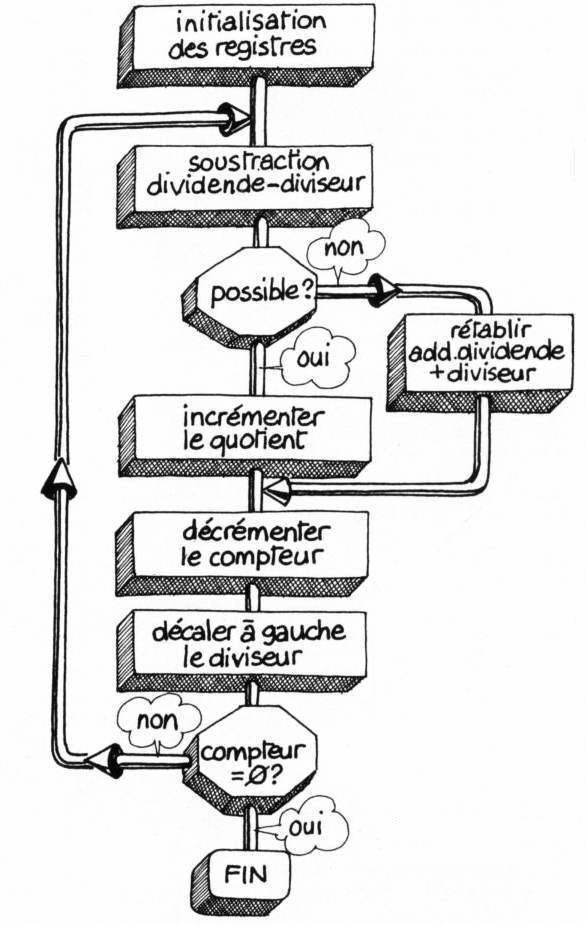

Une multiplication en binaire |  et maintenant une division |

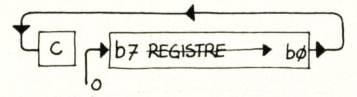

Étudions maintenant les opérations de rotation à l'aide d'exemples et de dessins appropriés :

D contient l'octet 11000010 et B l'octet 01000011

L'indicateur d'état est : C = 0

Remarque : avant l'étude de chaque cas. ces valeurs sont réinitialisées

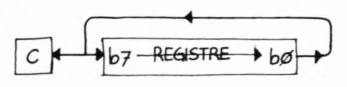

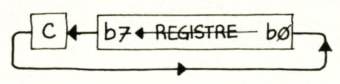

La rotation circulaire à gauche RLC

RLC D donne la valeur 1 000 0101 et l'indicateur d'état est : C = 1.

RLC B donne la valeur 1 000 0110 et l'indicateur d'état est C = 0

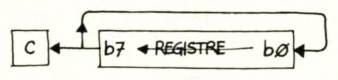

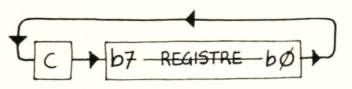

La rotation circulaire à droite RRC.

RRC D dônne la valeur 0110 0001 et l'indicateur d'état est C = 0

RRC B donne la valeur 1010 0001 et l'indicateur d'état est C = 1

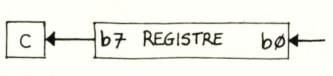

. La rotation à gauche RL

RL D donne la valeur 1000 0100 et C = 1 RL B donne la valeur 1000 0110 et C = 0.

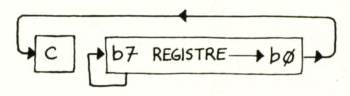

La rotation à droite RR

RR D donne la valeur 0110 0001 et C = 0

RR B donne la valeur 0010 0001 et C = 1

Ne nous arrêtons pas en si bon chemin et voyons maintenant en quoi consistent les opérations de décalage et les instructions correspondantes. Les registres D et B, l'indicateur d'état C sont initialisés ou réinitialisés comme précédemment

. Le décalage arithmétique à gauche SLA

SLA D donne la valeur 1000 0100 (1 32 d) et l'indicateur d'état C est égal à 1

SLA B donne la valeur 1000 0110 (134 d) et C = 0.

Les valeurs binaires du contenu des registres D et B sont respectivement 194 et 67 en système décimal Le résultat obtenu après SLA B est le double de la valeur initiale (soit 134 décimal). Le résultat obtenu après SLA D n'est pas égal au double de la valeur initiale : il y a eu retenue (indicateur d'état C 1). Dans ce cas, le résultat est égal au double de la valeur initiale diminué de la valeur 256 (c'est-à-dire 132).

Le décalage arithmétique à droite SRA

Un mot d'explication : le registre est décalé vers la droite comme poussé par le bit 7 qui se trouve ainsi recopié.

SRA D donne la valeur 11100001 (-31 en représentation complément à deux) et C = 0.

SRA B donne la valeur 00100001 (33) et C = 0.

L'instruction SRA divise par deux le contenu d'un registre; le reste, s'il existe, se trouve dans l'indicateur d'état C.

Le décalage à droite logique SRL

SRL D donne la valeur 01100001 (97 d) et C = 0

SRL B donne la valeur 0010 0001 (33 d) et C = 1.

Cette instruction est différente de la précédente uniquement parce qu'elle divise par deux l'octet en représentation binaire simple.

Le registre, dans le cas d'opérations de décalages et de rotations, peut être le contenu d'une adresse pointée (HL) ou indexée (IX, IY). Le décalage à gauche d'un demi-octet (RLD) et la rotation à droite d'un demi-octet (RRD) sont utilisés lors de la représentation en binaire codé décimal (BCD). Nous avons fait volontairement l'impasse sur cette représentation... pas tous les plaisirs en même temps !

Il faut encore signaler quatre autres instructions de rotations sur l'accumulateur :

Maintenant que nous avons passé en revue toutes les instructions de décalage et de rotations, revenons aux opérations arithmétiques avec l'étude de la multiplication et de la division.

La multiplication binaire suit le mode opératoire d'une multiplication décimale. Effectuons par exemple une multiplication dont le multiplicande est 00000101 (5 d.) et le multiplicateur 0000 0101 (5 d):

00000101 (5 d.)

x 00000101 (5 d.)

¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯

00000101

00000000

00000101

00000000...

¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯

00000011001 (25 d.)

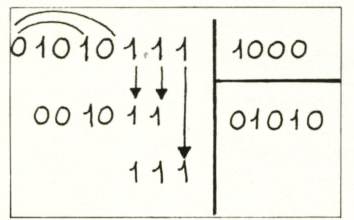

La division binaire n'est pas plus compliquée. Jugez-en vous-mêmes : prenons un exemple où le diviseur est 0000 1000 ( 8 d.) et le dividende 0101 0111 (87 d ):

Le quotient est la juxtaposition successive de bits 1 quand le diviseur « va » et de 0 quand le diviseur ne va pas. Ici le quotient obtenu est 1010. Si l'on ne peut plus «abaisser», la division est terminée. Cela donne le reste, 1 11 dans le cas présent Voir l'organigramme général d'une division en binaire page précédente.

Les opérations d'entrée / sortie sont spécifiques

Les instructions d'opérations d'entrées et de sorties permettent l'échange de données avec le « monde extérieur ». Ces « extra-mu-ros », appelés périphériques, peuvent être un clavier ASCII, un écran, un magnétophone, une imprimante, un capteur d'information (pression, température, contrôle d'un système...) ou un relais (asservissement d'une machine).

La rapidité des opérations d'entrées et de sorties de données entre le microprocesseur et l'extérieur dépend du mode de transfert de bits dans le bus : le bus parallèle transfère les données « de front ». Le raccordement avec un périphérique demande au minimum huit fils (S100, IEEE 488, IEEE 588). Le bus sériel transfère les données bit par bit. Le raccordement avec un périphérique demande un seul fil (deux en réalité pour des programmes d'adressage) pour le transfert des données

L'instruction de base pour les entrées de données est INA, (n). Une autre instruction, INR, (C), permet de charger le registre R (A, B, C, D, E. H ou L) d'un octet provenant du port entrée/sortie pointé par le registre C.

L'instruction INI permet l'entrée d'une donnée en mémoire ; pour cela, le registre HLdoit contenir l'adresse du début de bloc à charger, le registre B le nombre de données à traiter et le registre C l'adresse du port.

Le déroulement de l'opération s'effectue de la manière suivante : la donnée transmise par le périphérique est copiée dans la mémoire pointée par HL. HL est incrémenté et le compteur B décrémenté L'instruction INIR effectue les mêmes opérations de façon répétitive. Les instructions IND et INDR sont très voisines des précédentes: H L pointera l'adresse haute du bloc et, dans le déroulement des opérations, HL sera décrémenté.

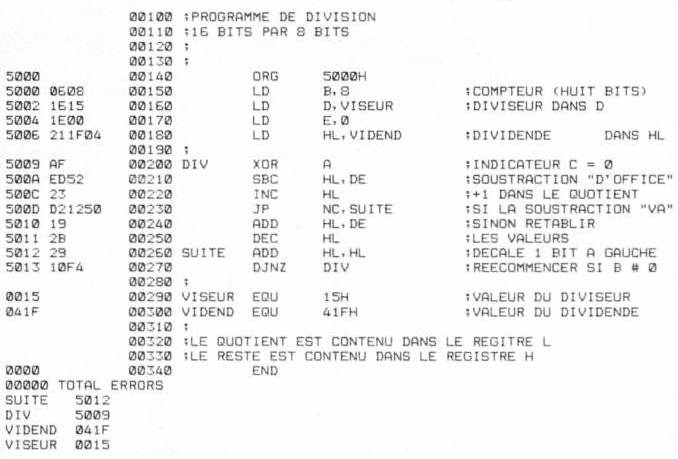

Liste E : une division binaire 16 bits par 8 bits:

L'instruction de base correspondant à la sortie de données est OUT (n), A. Parallèlement à INR,(C) il existe une instruction OUT (C), R Les instructions OUTI, OTIR, OUTD et OTDR agissent de la même manière que les instructions INI, INIR, IND et INDR ; dans ce cas les données sont transmises à un périphérique L'étude de ces instructions à l'aide d'exemples de programmes est fonction des adresses et de la structure des ports d'entrées et de sorties elle dépend donc de l'ordinateur utilisé.

Dans le cas du TRS 80, l'adresse du port Cassette est 0FFH ; la structure du port est la suivante

Et voilà ! nous sommes arrivés au terme de notre série d'articles sur l'assembleur.

Les notions exposées n'ont pas la prétention d'être exhaustives mais peut-être vous auront-elles donné l'envie d'en savoir plus.

« Le difficile, c'est ce qui peut être fait tout de suite; l'impossible, ce qui prend un peu plus de temps ». (G. Santayana).

Jean-Pierre Richard, L'Ordinateur individuel n°22

|  |

|

Page créée en 160 millisecondes et consultée 179 fois L'Amstrad CPC est une machine 8 bits à base d'un Z80 à 4MHz. Le premier de la gamme fut le CPC 464 en 1984, équipé d'un lecteur de cassettes intégré il se plaçait en concurrent du Commodore C64 beaucoup plus compliqué à utiliser et plus cher. Ce fut un réel succès et sorti cette même années le CPC 664 équipé d'un lecteur de disquettes trois pouces intégré. Sa vie fut de courte durée puisqu'en 1985 il fut remplacé par le CPC 6128 qui était plus compact, plus soigné et surtout qui avait 128Ko de RAM au lieu de 64Ko. |