2/3.1 - Le microprocesseur Z80Le Z80 est un microprocesseur LSI (Large Scale Intégration, ou intégration à grande échelle) 8 bits complètement compatible avec le 8080A (le Z80 accepte tous les ordres du 8080A) qui est né avant lui, il y a une dizaine d'années. Ces deux microprocesseurs ont été beaucoup utilisés, et sont encore beaucoup utilisés sur de petits systèmes industriels. Le Z80 a une capacité d'adressage de 64 Kilo-octets de mémoire RAM ou ROM grâce à son bus d'adresse de 16 bits {2ö = 65536, soit 64 Kilo-Octets). Son bus de données est de 8 bits, ce qui le classe dans la famille des micro-processeurs 8 bits. Sa fréquence d'horloge typique est de 4 MHz (Méga Hertz), ce qui lui confère une place confortable parmi les processeurs 8 bits du même type installés sur les micro-ordinateurs familiaux, qui, souvent, acceptent une fréquence d'horloge maximum de 1 ou 2 MHz. Sur les systèmes AMSTRAD CPC, le Z80 est cadencé par une horloge à 4 MHz, et adresse : - pour le CPC 464 : 64 KO de RAM et 32 KO de ROM,

- pour le CPC 664 : 64 KO de RAM et 48 KO de ROM,

- pour le CPC 6128 : 128 KO de RAM et 48 KO de ROM.

Ces capacités d'adressage dépassent les 64 KO possibles, et on a recours à un artifice appelé « pagination » pour dépasser le seuil fatidique des 64 KO.La pagination met en œuvre des pages mémoire (d'où son nom) couramment appelées banques RAM ou banques ROM suivant leur nature. Sur AMSTRAD, une banque fait 16 KO. A un moment donné, le microprocesseur pourra adresser 4 banques quelconques de mémoires RAM ou ROM. Pour adresser plus de 64 KO, il suffira de faire commuter les banques quand cela sera nécessaire (quand le Z80 voudra accéder à une banque différente des 4 courantes). Le Z80 possède 26 octets de mémoire RAM interne répartis dans les registres suivants : A F A' F'

B C B' C'

D E D' E'

H L H' L'Vecteur d'interruption I

Rafraîchissement mémoire R

Registres d'index IX et IY

Pointeur de pile SP

Compteur de programme PCPC Program Counter (ou compteur de programme) est un registre 16 bits qui pointe sur l'adresse de l'instruction courante. SP Stack Pointer (ou pointeur de pile) est un registre 16 bits qui donne l'adresse de la pile LIFO (Last In First Out, ou dernier entré premier sorti) située en RAM externe. Les instructions de manipulation de la pile sont POP (sortie de pile) et PUSH (mise en pile). La.désignation LIFO caractérise le type d'entrée/sortie des données dans un sspace mémoire appelé pile. La dernière donnée entrée par l'instruction PUSH est la première sortie par l'instruction POP. Ainsi, si vous faites : PUSH HL

PUSH BC PUSH IX

POP BC Le registre pair BC contiendra la dernière valeur mise en pile par l'instruction PUSH, c'est-à-dire la valeur contenue dans IX. Si vous refaites un POP, c'est BC qui sera dépilé, et si vous refaites un troisième POP, c'est HL qui sera dépilé.

Les piles gérées en interne par la logique des microprocesseurs sont pratiquement toujours du type LIFO. Cependant, il existe d'autres types de piles appelées LIFO et FIFO. La pile FILO (First In Last Out, ou premier entré dernier sorti) est assez rarement utilisée.

La pile FIFO (First In First Out, ou premier entré premier sorti) est surtout utilisée pour stocker des données que l'on ne peut pas traiter instantanément (pour des problèmes d'occupation du microprocesseur à d'autres tâches, par exemple). Ces données sont mémorisées, et la première donnée mémorisée est la première à être traitée. IX , IY Ce sont des registres 16 bits utilisés en adressage indexé. Ils donnent la base de l'adressage. Reportez-vous à la partie 4 chap. 2.2 pour avoir plus de détails à ce sujet. Nous ferons par exemple : LD A,(IX + 4)

Cette instruction charge dans le registre A le contenu de la mémoire pointée par l'adresse IX+ 4. I : Registre d'interruption qui donne la partie haute de l'adresse où doit se produire le débranchement en cas d'interruption. R : Registre de rafraîchissement. Il contient l'adresse basse qui sera mise

sur le bus d'adresse à chaque fois que le CPU est en train de lire et de décoder une instruction. Cette façon de procéder fait en sorte qu'aucune perte de temps n'est engendrée, puisque le bus est réquisitionné pour rafraîchir la mémoire pendant que le Z80 ne l'utilise pas. Ce registre est automatiquement incrémenté à chaque instruction. A : Accumulateur. C'est par lui que passent la plupart des opérations logiques ou arithmétiques sur 8 bits. Son accès est très rapide et les modes d'adressages qui le concernent sont multiples et variés. F : Flags (ou drapeaux). Ils donnent l'état de la dernière opération effectuée.

Les registres A et F peuvent être manipulés simultanément sous la forme du registre pair AF. Registres à usage général B, C, D, E, H et L sont des registres 8 bits qui peuvent être utilisés comme registres pairs (16 bits) sous les dénominations suivantes : BC, DE et HL. Ils possèdent leurs homonymes : - sur 8 bits : B', C, D', E', H' et L',

- sur 16 bits : BC, DE' et HL'.

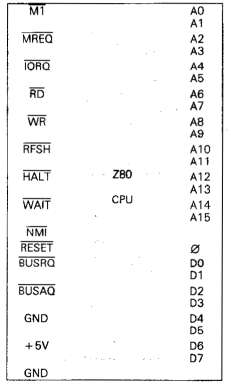

LE CIRCUIT INTÉGRÉ Z80C'est un circuit à 40 pattes dont le brochage est le suivant :

A0 à A15 : Bus d'adresse tristate en sortie actif à l'état haut sur 16 bits. AO est le bit le moins significatif (LSB), et A15 le bit le plus significatif (MSB). D0 à D8 : Bus de données tristate en entrée/sortie actif à l'état haut sur 8 bits. DO est le bit le moins significatif (LSB), et D7 le bit le plus significatif (MSB). M1 Sortie active à l'état bas, signale que le cycle horloge courant est consacré à une identification d'op-code, ou qu'un IORQ est actif. MREQ: Sortie tristate active à l'état bas. Signale que le bus d'adresse est en attente d'une adresse pour lire ou écrire en mémoire. IORQ : Sortie tristate active à l'état bas. Signale l'un des deux événements

suivants : - la partie de poids faible du bus d'adresse est en attente d'une adresse pour lire ou pour écrire en mémoire ;

- un vecteur d'interruption peut être placé sur le bus de données pour être acquis.

RD: Sortie tristate active à l'état bas. Signale que le CPU veut lire des données en mémoire ou sur un périphérique.WR: Sortie tristate active à l'état bas. Signale que le bus de données contient une donnée qui peut être stockée en mémoire ou envoyée vers un périphérique. RFSH : Sortie active à l'état bas. Indique que les 7 bits de poids faible du bus d'adresse contiennent une adresse de rafraîchissement des RAM dynamiques. HALT: Sortie active à l'état bas. Indique qu'une instruction HALT a été exécutée par le CPU. Ce dernier est en attente d'une interruption. Pendant ce temps, il exécute des NOP pour pouvoir rafraîchir ses RAM dynamiques. WAIT : Entrée active à l'état bas. Indique que la mémoire ou le périphérique n'est pas prêt à être accédé, INT : Entrée active à l'état bas. INT est générée par un périphérique pour signaler qu'iî désire qu'on s'occupe de lui. La requête prendra effet à la fin de l'exécution de l'instruction courante si te flag IFF est valide et si BUSRQ est inacttf. NMI : Entrée active sur front bas. Cette demande d'interruption est plus prioritaire que INT. Elle est prise en compte quel que soit l'état du flag IFF. Cette interruption débranche le CPU à l'adresse 0066H. Le PC est automatiquement sauvegardé, et la sortie d'interruption ramènera le PC à l'endroit où il avait été sauvegardé. RESET: Entrée active à l'état bas. Le PC est mis à 0 et le CPU est initialisé : IFF = 1, I = 0, R = 0, IM - 0. Pendant la phase de reset, les bus de données et d'adresses sont dans l'état tristate. BUSRQ: Entrée active à l'état bas. Sîgriale qu'un périphérique demande un accès aux bus de données, d'adresses et signaux de contrôles. Ces diverses pattes vont passer dans un état tristate. BUSAQ : Sortie active à l'état bas. Signale que les bus d'adresses, de données et les signaux de contrôle sont dans un état tristate, et que le périphérique qui a demandé de les contrôler peut le faire dès à présent. 0 : Horloge de cadencement du microprocesseur.

CPCrulez[Content Management System] v8.732-desktop/c

Page créée en 104 millisecondes et consultée 4050 foisL'Amstrad CPC est une machine 8 bits à base d'un Z80 à 4MHz. Le premier de la gamme fut le CPC 464 en 1984, équipé d'un lecteur de cassettes intégré il se plaçait en concurrent du Commodore C64 beaucoup plus compliqué à utiliser et plus cher. Ce fut un réel succès et sorti cette même années le CPC 664 équipé d'un lecteur de disquettes trois pouces intégré. Sa vie fut de courte durée puisqu'en 1985 il fut remplacé par le CPC 6128 qui était plus compact, plus soigné et surtout qui avait 128Ko de RAM au lieu de 64Ko. |

|