9/8.21 - Programmation du contrôleur de disquettes FDC-765, Check Disk pour lecteur de disquettesLes amoureux du langage machine et de la partie matérielle des CPC trouveront dans ce chapitre divers renseignements pour programmer le composant gestionnaire de l'unité de disquette FDC-765, et ainsi créer, pourquoi pas leurs disquettes personnalisées. Nous verrons aussi, qu'il est possible de programmer ce composant en langage Basic, relativement facilement, et vous proposerons par ailleurs un utilitaire de vérification de l'état de votre, ou vos, lecteur(s) de disquettes. Commençons par rappeler que vous pourrez trouver déjà, dans vos divers tomes, diverses informations sur le brochage du FDC-765 en Partie 2 Chapitre 3.5, le formattage des disquettes en Partie 4 Chapitre 1.6.5 (formatter une disquette sous Basic), et sur la lecture ou écriture des secteurs sur une disquette en Partie 9 Chapitre 5.8.10. Signalons aussi que toutes les explications données ci-après sont utilisables sur les CPC-664, CPC-6128, mais aussi sur les CPC-464 munis du contrôleur et du lecteur de disquettes de marque Amstrad. Les registres de travail du FDC-765 Pour dialoguer avec le microprocesseur, le contrôleur disquettes de l'Amstrad CPC ne possède que deux registres de travail accessibles sur Une adresse supplémentaire, ne concernant pas le FDC-765, mais directement en relation avec le lecteur de disquettes, est réservée à la commande de mise en marche et d'arrêt des moteurs des lecteurs de disquettes. Aussi, convient-il d'en décrire le fonctionnement ici. La commande des moteurs de disquettes La commande des moteurs de disquettes s'effectue par l'intermédiaire de l'adresse &FA7E. Le fait de transmettre la valeur 1 sur ce port met en route les moteurs de tous les lecteurs connectés à l'Amstrad, la valeur 0 (zéro) provoquant leur arrêt. Vous pouvez même essayer en Basic par les instructions : OUT &FA7E, 1 : REM MISE EN MARCHE MOTEURS

OUT &FA7E, 0 : REM ARRET DES MOTEURSLa programmation en assembleur s'effectuera par les instructions suivantes (à modifier selon la syntaxe de votre programme d'assemblage) : ;*** MISE EN MARCHE DES MOTEURS ***

LD A,01H ; VALEUR DE MISE EN MARCHE

LD BC,0FA7EH ; PORT MOTEUR

OUT (C),A ; MISE EN MARCHE;*** ARRET DES MOTEURS ***

LD A,00H ; VALEUR D'ARRET

LD BC,0FA7EH ; PORT MOTEUR

OUT (C),A ; ARRET Le registre d'état principal Accessible à tout moment par le microprocesseur, le registre d'état principal se trouve à l'adresse &FB7E, et n'est utilisable qu'en lecture. En Basic : A% = INP(&FB7F)

PRINT BIN$(A%,8)vous affichera la valeur binaire de ce registre. Ce registre permet de connaître l'état du contrôleur de disquette, par test de chacun de ses bits (voir figure 1).

Fig. 1 : Le registre d'état principal.

Le bit RQM (ReQuest for Master) permet de déterminer si le FDC est prêt à communiquer avec le microprocesseur, s'il est positionné à 1. Une valeur 0 signale que le FDC est occupé. Le bit DIO (Data Input Output) signale, lorsque le FDC est prêt à communiquer, le sens de transfert attendu. Positionné à 0, il signale que le FDC attend une donnée, sinon, à 1, qu'il a une donnée à fournir au microprocesseur. Le bit EXM (EXecution Mode) est positionné à 1, dans le cas du CPC, lorsque le FDC exécute un ordre qui lui a été transmis (transfert de données avec le support magnétique). Lorsqu'il est à zéro, il signale que, si le FDC fournit encore des données, celles-ci sont les données du compte rendu de l'exécution. Le bit CB (Contrôler Busy) signale en se positionnant à 1 que le FDC ne peut recevoir aucun nouvel ordre de la part du microprocesseur. DB3, DB2, DB1, DB0 (Disk Busy 3, 2, 1, 0) permettent de connaître l'état des lecteurs de disquettes connectés au FDC. Normalement, quatre lecteurs peuvent être connectés au composant, mais Amstrad a choisi, sur ses CPC de limiter ces connexions à 2. C'est donc en lisant le registre d'état principal qu'il sera possible de déterminer les différentes étapes de communications avec le FDC-765. Le registre de données Le registre de données du FDC-765 est accessible en lecture ou en écriture, et se trouve placé à l'adresse &FB7F. Ce registre permet de donner des instructions ou ordres au FDC, de lire ou écrire des données sur la disquette, et de connaître le résultat des ordres donnés. Trois phases seront donc réalisées, dans l'ordre suivant, à l'aide de ce registre : - la phase instruction : le microprocesseur fournit les octets au FDC ;

- la phase exécution : des données sont échangées entre le microprocesseur et le lecteur de disquettes, par l'intermédiaire du FDC (il arrive, selon les instructions qu'aucune donnée ne soit échangée, mais qu'une action ne soit réalisée par le lecteur de disquettes ;

- la phase résultat : le FDC fournit le bilan suite à l'exécution de l'instruction demandée.

Signalons que pour certaines instructions, la phase exécution et/ou la phase résultat n'existe pas. Les instructions du FDC Le microprocesseur doit en premier lieu envoyer au FDC un ordre qui se traduit par un numéro d'instruction, qui sera suivi, selon l'instruction de plusieurs octets d'information (jusque 8). Le code d'instruction Le contenu binaire de l'octet de codage de l'instruction envoyée au FDC est représenté en figure 2.

Fig.2 : Le code instruction.

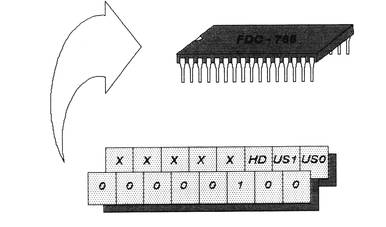

Le bit MT (Multi Track) lorsqu'il est positionné à 1 permet de prolonger l'exécution d'une instruction sur la deuxième face du lecteur de disquette, uniquement dans le cas des lecteurs possédant deux têtes (cette possibilité est utilisée par les DOS des lecteurs 700 k-octets, pas dans l'AMSDOS). Le bit MF (MFM) signale lorsqu'il est à un que le FDC-765 doit travailler en double densité. Le bit SK (SKip) permet, lorsqu'il est positionné à 1, d'ignorer les secteurs effacés sur la disquette. Les bits 14, 13, 12, 11 et 10 permettent de coder le numéro des instructions disponibles sur le FDC-765. Le code d'affectation Le code d'affectation suit, dans pratiquement toutes les instructions, sauf deux, l'octet de codage des instructions. Son contenu est représenté en figure 3.

Fig.3 : L'octet d'affectation des unités sélectionnées.

Le bit HD (HeaD select) permet de signaler le numéro de tête concernée par l'instruction. Il ne pourra, éventuellement, être à 1 que dans le cas des lecteurs double tête. Les deux bits US1 et US2 (Unit Select) permettent de sélectionner les lecteurs de disquettes : - 0 1 pour le lecteur B ;

- 1 0 pour le lecteur A.

Les instructions et leurs phases Comme nous l'avons expliqué précédemment, la plupart des traitements effectués par le FDC-765 suivent trois phases : instruction, exécution et résultat. Nous vous proposons ci-dessous d'étudier brièvement ces trois phases. Vous y découvrirez, notamment dans la phase résultat, que quatre registres d'état peuvent être fournis par le FDC : les registres 0, 1, 2 et 3, que nous détaillerons après l'étude des instructions. • Le paramétrage des lecteurs Cette instruction ne comporte que la phase instruction (voir figure 4), qui consiste à envoyer successivement le code de l'instruction (00000011), les temps d'impulsions de position de tête (STEP RATE) et d'élévation de tête (uniquement sur les lecteurs 8 pouces), puis le délai de chargement de la tête. Il est aussi possible de commander le fonctionnement du FDC en mode DMA (Direct Memory Access = accès direct à la mémoire), mais celui-ci n'est pas prévu dans le fonctionnement sur CPC.

Fig.4 : Paramètres à fournir pour spécifier les données du lecteur de disquettes.

Cette instruction est la toute première instruction nécessaire au FDC pour paramétrer le(s) lecteur(s) avec lesquels il va travailler. Cette opération est réalisée dès l'initialisation de l'AMSDOS. • Le formattage d'une piste Représentée en figure 5, la phase instruction du FDC-765 pour format-ter une piste nécessite six octets.

Fig.5 : Paramètres à fournir pour l'exécution d'une instruction de formattage d'une piste.

La phase exécution consiste à formatter la piste positionnée sous la tête, en tenant compte des informations fournies. Une fois la piste formattée, le FDC-765 va entrer dans sa phase résultat, qui consiste à envoyer dans l'ordre (voir figure 6), les octets suivants : - l'octet du registre d'état numéro 0 ;

- l'octet du registre d'état numéro 1 ;

- l'octet du registre d'état numéro 2 ;

- le numéro de la piste ;

- le numéro de tête ;

- un numéro de secteur ;

- une taille de secteur.

Fig. 6 : Les sept octets fournis par le FDC après exécution de l'instruction.

• L'identification de formattage La figure 7 représente les deux octets de la phase instruction d'identification.

Fig. 7 : Paramètres à fournir pour l'exécution d'une instruction de lecture d'identification de formattage.

La phase exécution consistera à lire et fournir aux registres de données la prochaine identification. La phase résultat est identique à celle représentée en figure 6. • Le positionnement sur la piste zéro Deux octets seulement sont à fournir lors de la phase instruction (voir figure 8).

Fig.8 : Paramètres à fournir pour l'exécution d'une instruction de positionnement sur la piste 0.

La phase exécution consistera à déplacer la tête sur la périphérie de la disquette pour la positionner sur la piste zéro. Pas de phase résultat. • L'interrogation de l'état d'un lecteur La phase instruction nécessite deux octets (voir figure 9).

Fig. 9 : Paramètres à fournir pour l'exécution d'une instruction de demande d'état d'un lecteur.

Le FDC-765 renvoi ensuite le contenu du registre numéro 3 (voi figure 10), spécifiant les caractéristiques du lecteur, que nous étudie rons dans le détail plus loin.

Fig. 10 : Octet résultat fournit par le FCD après exécution de l'instruction de demande d'état du lecteur de disquettes.

• Le positionnement sur une piste particulière La phase instruction est représentée en figure 11.

La phase exécution consiste à déplacer la tête sur la piste requise.

Fig. 11 : Paramètres à fournir pour l'exécution d'une instruction de positionnement sur une piste.

La phase exécution consiste à déplacer la tête sur la piste requise. Il n'y a pas de phase résultat. • La lecture d'une piste complète La phase instruction est représentée en figure 12.

Fig. 12 : Paramètres à fournir pour l'exécution d'une instruction de lecture d'une piste par le FDC-765.

La phase exécution consiste à transférer le contenu complet de la piste sous la tête, depuis le trou d'index, jusqu'à la rencontre du dernier secteur, ou de la détection pour la deuxième fois du trou d'index. La phase résultat est identique à celle de la figure 6. • La lecture d'un secteur La phase instruction est représentée en figure 13.

Fig. 13 : Paramètres à fournir pour l'exécution d'une instruction de lecture par le FDC-765.

La phase exécution consiste à transférer vers le microprocesseur les données d'un secteur donné. La phase résultat est identique à celle de la figure 6. • L'écriture d'un secteur La phase instruction est représentée en figure 14.

Fig. 14 : Paramètres à fournir pour l'exécution d'une instruction d'écriture par le FDC-765.

La phase exécution consiste à transférer sur le support magnétique, vers le secteur concerné, le contenu d'un secteur fourni par le microprocesseur au FDC. La phase résultat est identique à celle de la figure 6. • La lecture d'un secteur effacé La phase instruction est représentée en figure 15.

Fig. 15 : Paramètres à fournir pour l'exécution d'une instruction de lecture de données effacées par le FDC-765.

La phase exécution consiste à transférer vers le microprocesseur les données déclarées d'un secteur effacé. La phase résultat est identique à celle de la figure 6. • L'écriture d'un secteur effacé La phase instruction est représentée en figure 16.

Fig. 16 : Paramètres à fournir pour l'exécution d'une instruction d'écriture de données effacées par le FCD-765.

La phase exécution consiste à transférer sur le support magnétique le contenu d'un secteur en le marquant effacé. • Les tests de secteurs Les trois phases instructions de chacun des tests possibles (égalité de secteur, secteur inférieur ou égal, ou secteur supérieur ou égal) sont représentées, respectivement en figures 17, 18 et 19.

Fig. 17 : Paramètres à fournir pour l'exécution d'une instruction de test d'égalité sur un secteur.

Fig. 18 : Paramètres à fournir pour l'exécution d'une instruction de test d'infériorité (ou égal) sur un secteur.

Fig. 19 : Paramètres à fournir pour l'exécution d'une instruction de test de supériorité (ou égal) sur un secteur. La phase exécution consiste à prendre un à un les octets du secteur spécifié, et de les comparer avec chacune des données, réclamées une à une aussi, au microprocesseur. La phase résultat est identique à celle de la figure 6. • La demande d'état des interruptions La phase instruction est représentée en figure 20.

Fig. 20 : Paramètres à fournir pour l'exécution d'une instruction de demande d'état d'interruption.

Il n'y a pas de phase exécution. La phase résultat est représentée en figure 21.

Fig. 21 : Octets résultat fourni par le FDC après exécution de l'instruction de demande d'état d'interruption.

Les registres d'état de la phase résultat • Le registre 0 Ce registre est fournit suite à une demande d'état d'interruption, et est affecté à chaque fois qu'une modification concernant le lecteur de disquette apparaît. Son contenu est spécifié en figure 22. Les bits ICI et ICO (Interrupt Code) indiquent l'état de déroulement d'une instruction : ICI ICO = 11: apparaît lors d'un défaut sur un lecteur de disquette, ou du retrait d'une disquette d'un lecteur concerné par une instruction. ICI ICO = 10 : signale que l'instruction envoyée au FDC-765 n'est pas légale, ou encore que la demande d'état d'interruption n'a pas lieu d'être car aucune interruption n'est apparue. ICI ICO = 01 : apparaît lorsqu'une instruction n'a pas pu s'effectuer correctement. ICI ICO = 00 : indique qu'une instruction a été correctement exécutée. Le bit SE (Seek End) est placé à 1 dès qu'une instruction est terminée. Le bit EC (Equipment Check) est placé à 1 si le lecteur de disquette est positionné en erreur. Le bit NR (Non Ready) est placé à 1 lors de l'exécution d'une instruction de lecture ou d'écriture alors que le lecteur de disquette n'est pas prêt. Le bit HD est l'image de la tête en cours de sélection (0 pour la tête numéro 0 et 1 pour la tête numéro 1). Les bits US1 et US0 indiquent le numéro de lecteur actif lors de l'apparition de l'interruption (voir le paragraphe concernant le code d'affectation des instructions). • Le registre 1 Ce registre informe sur le déroulement de la phase exécution (voir son contenu en figure 23).

Fig. 23 : Le registre d'état 1.

Le bit EN (ENd) est placé à 1 lorsque le FDC-765 essaie de lire un secteur alors que la fin de la piste est dépassée. Le bit DE (Data Error) indique que la donnée lue sur le support magnétique n'est pas valable. Le bit OR (Over Run) est placé à 1 lorsque le microprocesseur n'a pas lu assez rapidement les données fournies par le FDC (lorsqu'une donnée est fournie par le FDC alors que la précédente n'a pas été lue). Le bit ND (No Data) est positionné à 1 lorsque le FDC ne trouve pas le secteur recherché, ou y trouve une erreur. Le bit NW (Non Writable) est mis à 1 lorsque la disquette est protégée et qu'une instruction d'écriture ou de formattage est demandée au FDC-765. Le bit MA (Missing Adress mark) est mis à 1 lorsque le FDC n'a pas trouvé l'identification d'un secteur demandé en écriture ou en lecture. • Le registre 2 Ce registre complémente le registre 1, et a donc la même fonction. Son contenu est représenté en figure 24.

Fig. 24 : Le registre d'état 2.

Le bit CM (Control Mark) est placé à 1 lorsque le FDC rencontre une Data Adresse Mark effacée. Le bit DD (Data error in Data field) indique une erreur sur une donnée lue dans un champ de données. Le bit WC (Wong Cylender) est mis à 1 lorsque le numéro lu sur la piste est la piste indiquée dans la phase instruction. Le bit SH (Scan equal Hit) est à 1 lors de l'exécution d'une instruction de test d'un secteur, si les données comparées sont identiques. Le bit SN (Scan Not satisfed) est placé à 1 dans le cas contraire au bit SH. Le bit BC (Bad Cylinder) est mis à 1 lors d'une erreur d'identification de piste. Le bit MD (Missing adress mark in Data field)est mis à 1 lorsque le FDC ne trouve pas de Data Adress Mark dans un champ de données. • Le registre 3 Ce registre permet, par l'intermédiaire de l'instruction de demande d'état d'un lecteur de disquettes d'en connaître ses caractéristiques (voir figure 25).

Fig. 25 : Le registre d'état 3.

Le bit FT (FaulT) signale que le lecteur de disquettes indique une erreur. Le bit WP (Write Protected) est mis à 1 lorsque la disquette dans le lecteur est protégée contre l'écriture. Le bit RY (ReadY) est mis à 1 lorsque le lecteur de disquettes est prêt à être utilisé (lorsqu'une disquette s'y trouve surtout). Le bit TO (Track 0) est mis à 1 si la tête du lecteur de disquettes se trouve sur la piste 0. Le bit TS (Two Sides) est mis à 0 (zéro) si le lecteur de disquettes testé possède deux têtes. Le bit HD (HeaD select) signale l'état de la broche Head Select. Les bits US1 et USO indiquent le numéro du lecteur testé. Utilisation sous Basic : un Check Disk Vous connaissez peut-être l'instruction CHKDSK des Disk Operating System (DOS) des ordinateurs compatibles PC, qui étudie les caractéristiques d'un lecteur de disquette ou d'un disque dur. Nous vous proposons ici un programme s'en rapprochant, qui détermine l'état des lecteurs de disquettes de votre Amstrad CPC. Ce programme utilise le registre 3 du FDC en envoyant une demande d'état sur les deux lecteurs de disquettes possibles du CPC. L'écran fera apparaître pour chaque lecteur : - son numéro (A ou B) ;

- un défaut s'il y a ;

- la présence d'une disquette ;

- l'état de la disquette insérée (protégée ou non).

Le listing commenté est le suivant : [INCOMPLET] On remarquera qu'avant d'exécuter l'instruction, le moteur du lecteur concerné est mis en marche, et qu'une temporisation est lancée. On ne compte le lecteur que quand la phase résultat est lue complètement. Le registre d'état principal est aussi utilisé avant chaque écriture ou lecture pour connaître l'état du FDC.

CPCrulez[Content Management System] v8.7-desktop/c

Page créée en 308 millisecondes et consultée 1108 foisL'Amstrad CPC est une machine 8 bits à base d'un Z80 à 4MHz. Le premier de la gamme fut le CPC 464 en 1984, équipé d'un lecteur de cassettes intégré il se plaçait en concurrent du Commodore C64 beaucoup plus compliqué à utiliser et plus cher. Ce fut un réel succès et sorti cette même années le CPC 664 équipé d'un lecteur de disquettes trois pouces intégré. Sa vie fut de courte durée puisqu'en 1985 il fut remplacé par le CPC 6128 qui était plus compact, plus soigné et surtout qui avait 128Ko de RAM au lieu de 64Ko. |

|