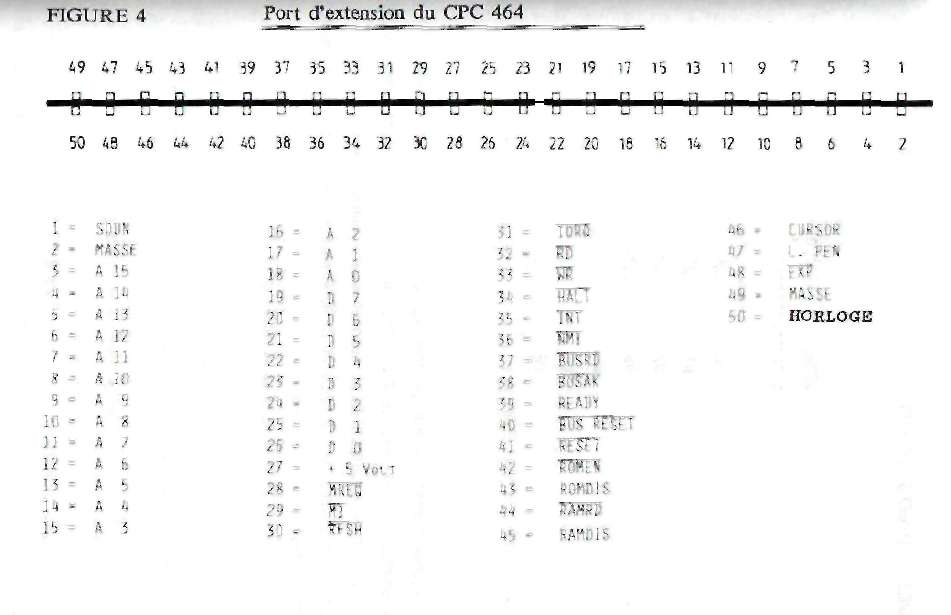

4. PORT D'EXPANSIONTous les signaux importants utilisés dans l'ordinateur se retrouvent sur l'un des connecteurs en face arrière. Nous nous intéresserons plus particulièrement au port d'expansion, un port à 50 broches, que nous utiliserons pour presque toutes nos extensions. Vous trouverez son brochage en figure 4. A coté des 8 lignes de données et des 16 lignes d'adresses on retrouve tous les signaux du CPU ainsi que la tension d'alimentation. Dans ce qui suit, la fonction des principaux signaux sera décrite, vous permettant de comprendre leurs applications possibles dans les différentes extensions. Vous trouverez d'autres compléments au chapitre 28 où est décrit le fonctionnement du CPC 464. Les lignes utilisées pour les extensions peuvent se regrouper en trois familles: - Lignes d'adresses et de données

- Lignes véhiculant les signaux du CPU

- Lignes spéciales

LIGNES DE DONNEES D0 - D7 ligne ; broche

-------------------------------

D0 ; 26

D1 ; 25

D2 ; 24

D3 ; 23

D4 ; 22

D5 ; 21

D6 ; 20

D7 ; 19Ces lignes forment le BUS de données et véhiculent les données en provenance de-, et vers le Z-80 CPU. Tous les signaux sont compatibles TTL, il est donc possible d'y connecter une charge TTL-LS. Toutes les lignes de données sont des entrées/sorties trois états (tri-state).LIGNES D'ADRESSES A0 - A15 ligne ; broche

-------------------------------

A0 ;18

A1 ;17

A2 ;16

A3 ;15

A4 ;14

A5 ;13

A6 ;12

A8 ;10

A9 ; 9

A10 ;8

A11 ;7

A12 ;6

A13 ;5

A14 ;4

A15 ;3Les 16 bits d'adresses (A0 - A15) permettent d'adresser la mémoire de l'ordinateur. Il est ainsi possible d'adresser au maximum:2 puissance 16 = 65536 octets = 64K Toutes les broches du BUS d'adresses sont des sorties a trois états. Les 8 bits de poids faible (A0 - A7) servent également a l'adressage des entrées/sorties; il est possible d'adresser directement 2 puis. 8= 256 entrées/sorties. Pendant le cycle de rafraîchissement des RAMs, ces mêmes bits A0 - A8 contiennent les adresses â rafraîchir, Toutes les adresses sont compatibles TTL. ALIMENTATION potentiel broche

------------------

+ 5 V 27

0 V 2 & 49Malheureusement, et contrairement à d'autres ordinateurs comme par exemple le ZX-Spectrum, se sont les seules tensions présentes sur le port d'expansion. Celui qui veut connecter des extensions doit avant tout se fabriquer une alimentation,

La tension de 5 Volt présente sur la broche 27 peut au maximum délivrer un courant de 300 mA, sinon le régulateur interne au CPC serait surchargé.4.1. Lignes de signaux CPU On peut diviser ces signaux en trois sous-ensembles : - Contrôle du système

- Contrôle du CPU

- Contrôle de BUS

1. CONTROLE DU SYSTEME1-1. RD, (Read: lire), broche 32 En mode lecture cette broche a le niveau 0 lorsque l'ordinateur doit lire des données dans la mémoire ou sur une entrée.

Dans ce cas les données sont écrites sur le BUS de données par le circuit adressé. Dans l'état non actif, cette ligne est au niveau 1 (5 Volt). 1.2. WR, (Write: écrire), broche 33 Le mode écriture est similaire au précédent. La sortie se trouve au niveau 0 lorsque le CPU envoie des données vers l'extérieur.

Dans ce cas la mémoire ou le port adressé se tient prêt à recevoir les données. 1.3. MREG, (Memory Request: demande d'accès mémoire), broche 28 Avant chaque accès à la mémoire il faut s'assurer que le système est prêt/ c.à.d. s'il se trouve bien une adresse sur le BUS d'adresses; si c'est le cas les opérations read ou write peuvent débuter. Un niveau 0 sur la broche 28 indique que tout est en ordre. 1.4. IORQ, (In Out Request: demande d'entrée/sortie), broche 31 La fonction est ici la même que pour MREQ avec la différence qu'il s'agit ici d'opérations d'entrée/sortie.

Un niveau 0 sur la broche indique que le CPU désire envoyer ou lire une donnée sur un port. Dans ce cas les bits A0 - A7 contiennent l'adresse du port souhaité. Le signal 141 (cycle machine 1) déclenche lui-même un signal IORQ lorsqu'une interruption a été validée. Les opérations de validation d'interruption s'effectuent pendant le temps M1; pour cette durée aucune opération d'entrée/sortie n'est possible. 1.5. RFSH, (Refresh: rafraîchissement), broche 30 Cette sortie concerne le rafraîchissement des RAMs dynamiques. Un niveau 0 indique que le cycle de rafraîchissement peut commencer; les 7 premiers bits de l'adresse à rafraîchir sont contenue sur le BUS de données. Cette broche travaille en liaison avec MREQ, de telle sorte qu'un rafraîchissement peut immédiatement être suivi par une lecture mémoire. 1.6. M1, (cycle machine), broche 29 Ce signal ne présente que peu d'intérêt pour les applications externes. Un niveau 0 signifie que le cycle machine en cours est en train de lire un code opératoire dans la mémoire. Cette broche devient également active (niveau 0) en liaison avec IORQ, lorsque le CPU confirme une demande d'interruption. 1.7. ROMEN , (ROM-ENable) , broche 42

ROMDIS, (ROM-DISable) , broche 43 Il s'agit ici de signaux Chip-Select pour des ROMs externes (pour plus de détails voir chapitre 28). 1.8. RAMDIS, (RAM-DISable), broche 45

RAMRD , ( RAM-Read ) , broche 44 Ici c'est un signal Chip-Select pour des RAMs externes, ainsi que le signal de lecture correspondant. 2. Contrôle du CPU 2.1. HALL (pause), broche 34 Cette sortie devient active lorsque le CPU exécute un HALT programmé, Il reste en attente jusqu'à la prochaine demande d'interruption. Le rafraîchissement continue néanmoins d'avoir lieu pendant cette pause. 2.2. INT, (demande d'interruption), broche 35 Ici encore ce signal n'interviendra pas dans nos extensions. L'entrée du CPU est commandée par les circuits d'entrée/sortie. Lorsque le niveau passe à 0, le programme est interrompu après l'exécution de l'instruction en cours, à la condition qu'un EI l'y ait autorisé auparavant.

Lorsque le CPU prend en compte la demande d'interruption, il retourne

un signal de confirmation. 2.3. NMI, (Non Maskable Interrupt: interruption non mascable), broche 36 Cette entrée d'interruption a priorité sur INT et ne peut être inhibé par un DI. Après avoir terminé l'exécution de l'instruction en cours, le CPU se branche à l'adresse 0066 (hexa.). Ce signal n'intéresse pas les applications externes. 2.4. RESET, (initialise), broche 41 Avec se signal l'ordinateur peut â tout instant être mis dans un état prédéfini. Un niveau 0 met le CPC dans le même état qu'il se trouve à

l'allumage (se branche à l'adresse 0).

CPCrulez[Content Management System] v8.732-desktop/c

Page créée en 084 millisecondes et consultée 2752 foisL'Amstrad CPC est une machine 8 bits à base d'un Z80 à 4MHz. Le premier de la gamme fut le CPC 464 en 1984, équipé d'un lecteur de cassettes intégré il se plaçait en concurrent du Commodore C64 beaucoup plus compliqué à utiliser et plus cher. Ce fut un réel succès et sorti cette même années le CPC 664 équipé d'un lecteur de disquettes trois pouces intégré. Sa vie fut de courte durée puisqu'en 1985 il fut remplacé par le CPC 6128 qui était plus compact, plus soigné et surtout qui avait 128Ko de RAM au lieu de 64Ko. |

|