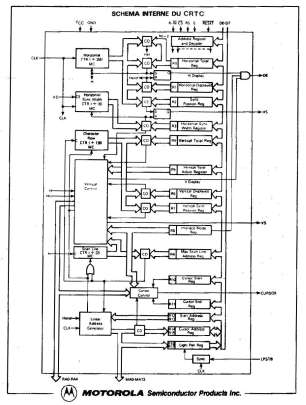

2/3.2.1 -CRT Controller ou CRTCLe circuit CRTC de référence MC 6845 proposé par MOTOROLA est un circuit intégré à haute intégration comportant 40 broches, dont la fonction est la génération des signaux nécessaires pour produire une image qui sera affichée sur l'écran cathodique d'un moniteur ou d'un téléviseur. L'organisation interne de ce circuit est la suivante : (Voir schéma page suivante.)

Nous voyons que le CRTC contient 19 registres. Ces registres sont chargés automatiquement par l'AMSTRAD au moment où vous le mettez sous tension. Ils ne doivent pas être modifiés sauf si vous désirez créer des effets spéciaux ou interfacer un light-pen. Leur utilisation est la suivante : AR = ADDRESS REGISTER

(Registre d'adresse) Ce registre est accédé à travers le bus de données. Il permet de sélectionner un des 18 registres internes (R0 à R17). - Quand RS = 0 et CS = 0, le registre d'adresse est accessible.

- Quand RS = 1 et CS = 0, te registre pointé par AR est accessible.

Click pour zoomer R0 = HORIZONTAL TOTAL REGISTER

(Fréquence horizontale totale) Ce registre 8 bits à écriture seule définit la fréquence de synchronisation horizontale : temps nécessaire pour afficher une ligne horizontale + temps nécessaire pour le retour du spot -1. R1 = HORIZONTAL DISPLAYED REGISTER

(Nombre de caractères affichés par ligne) Ce registre 8 bits à écriture seule définit le nombre de caractères affichés par ligne.

Remarque : R1 doit être inférieur ou égal à R0. R2 = HORIZONTAL SYNC POSITION REGISTER

(Synchronisation horizontale) Ce registre 8 bits à écriture seule permet de contrôler la synchronisation horizontale : délai de synchronisation (front porch) et délai de balayage horizontal (back porch). Remarque : R2 doit être inférieur ou égal à R0 et supérieur à R1. R3 = SYNC WIDTH REGISTER

(Largeur de la synchronisation horizontale) Ce registre 8 bits à écriture seule dont 4 bits seulement sont utiles définit la largeur du top de synchronisation horizontale. Il doit avoir une valeur comprise entre 1 et 15. Il est exprimé en multiple du nombre de périodes d'horloge nécessaires à l'affichage d'un caractère. R4 = VERTICAL TOTAL REGISTER

(Nombre de lignes par écran) Ce registre 8 bits à écriture seule dont 7 bits seulement sont utiles détermine le nombre entier de lignes de caractères - 1 à partir duquel sera calculée la fréquence de synchronisation verticale. R5 = VERTICAL TOTAL ADJUST REGISTER

(Ajustage du nombre de lignes par écran) Ce registre 8 bits à écriture seule dont 5 bits seulement sont utiles détermîne le nombre de lignes de tramés à ajouter à R4 pour calculer la fréquence de synchronisation verticale. R6 = VERTICAL DISPLAYED REGISTER

(Nombre de lignes affichées à l'écran) Ce registre 8 bits à écriture seule dont 7 seulement sont utiles définit le nombre de lignes de caractères affichés à l'écran.

Remarque : R6 doit être inférieur à R4. R7 = VERTICAL SYNC POSITION

(Synchronisation verticale) Ce registre 8 bits à écriture seule dont 7 seulement sont utiles permet de contrôler la synchronisation verticale. Il définit le nombre de lignes de trames à balayer avant d'activer le signal VSYNC.

Remarque : R7 doit être inférieur à R4 et supérieur à R6. R8 = INTERLACE MODE AND SKEW REGISTER

(Mode normal ou interlacé) Ce registre 8 bits dont 2 seulement sont utiles permet de définir le mode

de fonctionnement du CRTC : Bit0 Bit 1 Fonction

------------------------------------------

0/1 0 Mode normal (non entrelacé)

0 1 Mode entrelacé

1 1 Mode entrelacé et vidéoLes modes définis ci-dessus ont la signification suivante :

Par exemple, sur la lettre T : ; 000000

000000 ;000000 ;000000

; 000000 ;00

00 ; 00 ; 00

; 00 ; 00

00 ; 00 ; 00

; 00 ; 00

00 ; 00

; 00

00 ; 00

; 00

00 ; 00

; 00

00 ; 00

Mode normal Mode entrelacé Mode entrelacé

; et vidéoR9 = MAXIMUM SCAN UNE ADDRE5S REGISTER

(Nombre de lignes élémentaires par caractère) Ce registre 8 bits à écriture seule dont 5 bits sont utiles permet de définir le nombre de lignes élémentaires par caractère - 1. R10 = CURSOR START REGISTER

(Début du curseur) Ce registre 8 bits à écriture seule dont 7 bits sont utiles permet de définir la position de la première ligne élémentaire du curseur (bits 0 à 4) et la vitesse de clignotement du curseur. Les bits 5 et 6 définissent la vitesse de clignotement comme suit : Bit 6 Bit 5 ;Fonction

-------------------------------------------------

0 ;0 ; Pas de clignotement

0 ;1 ; Curseur invisible

1 ;0 ; Clignotement lent

1 ;1 ; Clignotement rapideR11 = CURSOR END REGISTER

(Fin du curseur) Ce registre 8 bits à écriture seule dont 5 bits sont utiles permet de définir la position de la dernière ligne élémentaire du curseur (bits 0 à 4). R12-R13 = START ADDRESS REGISTER

(Adresse de la RAM d'écran) Registres à lecture/écriture.

Première adresse de la RAM d'écran affichée après un « vertical blanking ». Les 6 bits de poids faible de R12 donnent le poids fort de cette adresse, et les 8 bits de R13 le poids faible de cette adresse. R14-R15 = CURSOR REGISTER

(Position du curseur) Registres à lecture/écriture.

Permet de positionner le curseur n'importe où sur l'écran. Les 6 bits de poids faibles de R14 donnent le poids fort de l'adresse, et les 8 bits de R15 le poids faible de l'adresse. R16-R17 - LIGHT-PEN REGISTER

(Position du light-pen) Registres à lecture seule.

Permet de connaître la position du light-pen sur l'écran.

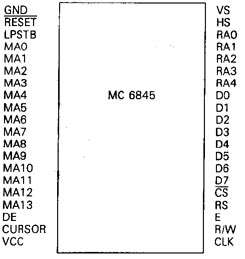

Les 6 bits de poids faible de R17 donnent le poids fort de l'adresse, et les 8 bits de R16 le poids faible de l'adresse. LE CIRCUIT INTÉGRÉ MC 6845

C'est un circuit à 40 pattes dont le brochage est le suivant :

D0 à D7:

(DATA BUS ou bus de données). Bus de données bidirectionnel tristate entre CTRC et micro-processeur. E:

(ENABLE ou validation). Signal tristate compatible avec la logique TTL et CMOS. Un front descendant sur cette broche valide les données présentes sur le bus de données. CS:

(CHIP SELECT ou validation du circuit). Signal tristate compatible avec la logique TTL et CMOS. Quand ce signal est bas, l'accès au CRTC est valide : les registres internes peuvent être lus ou écrits. RS :

(REGISTER SELECT ou sélection de registre). Signal tristate compatible avec la logique TTL et CMOS. Si RS = 0, le registre d'adresse peut être sélecte, si RS = 1, le registre de données ou un registre interne peut être sélecte. R/W:

(READ/WRITE ou lecture/écriture). Signal tristate compatible avec la logique TTL et CMOS. Détermine si les registres internes vont être accèdes en lecture ou en écriture. VS e tHS:

(VERTICAL SYNC and HORIZONTAL SYNC ou synchronisations verticale et horizontale). Sorties compatibles avec la logique TTL actives à l'état haut. Ces signaux sont destinés au processeur vidéo pour générer un signal composite. DE:

(DISPLAY ENABLE ou affichage valide). Sortie compatible avec la logique TTL active à l'état haut. Indique si le CRTC est en train de manipuler une adresse en RAM écran. MA0 à MA13:

(REFRESH MEMORY ADDRESSES ou adresses de rafraîchissement de mémoire d'écran). Sorties destinées au rafraîchissement des mémoires RAM écran par bloc de 16 KO (Kilo-Octets). RA0 & RA4:

(ROW ADDRESSES ou adresses de lignes). Sorties destinées à lire les caractères à afficher dans la ROM du générateur de caractères. CURSOR :

Sortie compatible avec la logique TTL active à l'état haut. Indique qu'une adresse valide est disponible pour la logique vidéo externe. CLK:

(CLOCK ou horloge). Entrée comptabile avec la logique TTL et CMOS active sur un front descendant. Permet de synchroniser toutes les fonctions d'écran. LPSTB :

(LIGHT PEN STROBE ou lecture de la position du stylo lumineux). Un front descendant sur cette broche positionne l'adresse courante de rafraîchissement de RAM d'écran dans le registre « light pen ». VCC et VSS :

Alimentation du CRTC : VCC = 5V ± 5%. VSS = 0V. RESET :

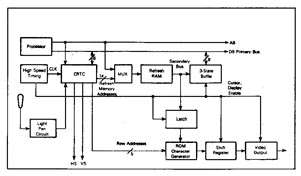

Un niveau bas sur cette broche permet d'effacer le contenu de tous les registres internes du CRTC. Le CRTC s'interface avec les divers circuits d'un ordinateur de la manière suivante :

Click pour zoomer

CPCrulez[Content Management System] v8.7-desktop/c

Page créée en 492 millisecondes et consultée 4216 foisL'Amstrad CPC est une machine 8 bits à base d'un Z80 à 4MHz. Le premier de la gamme fut le CPC 464 en 1984, équipé d'un lecteur de cassettes intégré il se plaçait en concurrent du Commodore C64 beaucoup plus compliqué à utiliser et plus cher. Ce fut un réel succès et sorti cette même années le CPC 664 équipé d'un lecteur de disquettes trois pouces intégré. Sa vie fut de courte durée puisqu'en 1985 il fut remplacé par le CPC 6128 qui était plus compact, plus soigné et surtout qui avait 128Ko de RAM au lieu de 64Ko. |

|